## **User's Guide**

# NHD-0108FZ-RN-YBW LCM

## (Liquid Crystal Display Module) RoHS Compliant

NHD- Newhaven Display0108- 1 Lines x 08 Characters

FZ- Version Line

R - Reflective

N- No LED B/L

V- STN Vellow/Green

Y- STN-Yellow/Green

**B-** 6:00 View

W- Wide Temperature  $(-20 \sim +70c)$

-For product support, contact

Newhaven Display International, LLC 2511 Technology Drive, #101 Elgin, IL 60124

Tel: (847) 844-8795 Fax: (847) 844-8796

## **NHD-0108FZ**

## SPECIFICATION OF LCD MODULE

#### **Features**

- 1. 5x8 dots with cursor

- 2. Built-in controller (KS0066U or equivalent)

- 3. +5V power supply (also available for =3.0V)

- 4. 1/8 duty cycle

- 5. BKL to be driven by pin1, pin2, or pin15, pin16 or A, K

- 6. N.V. optional

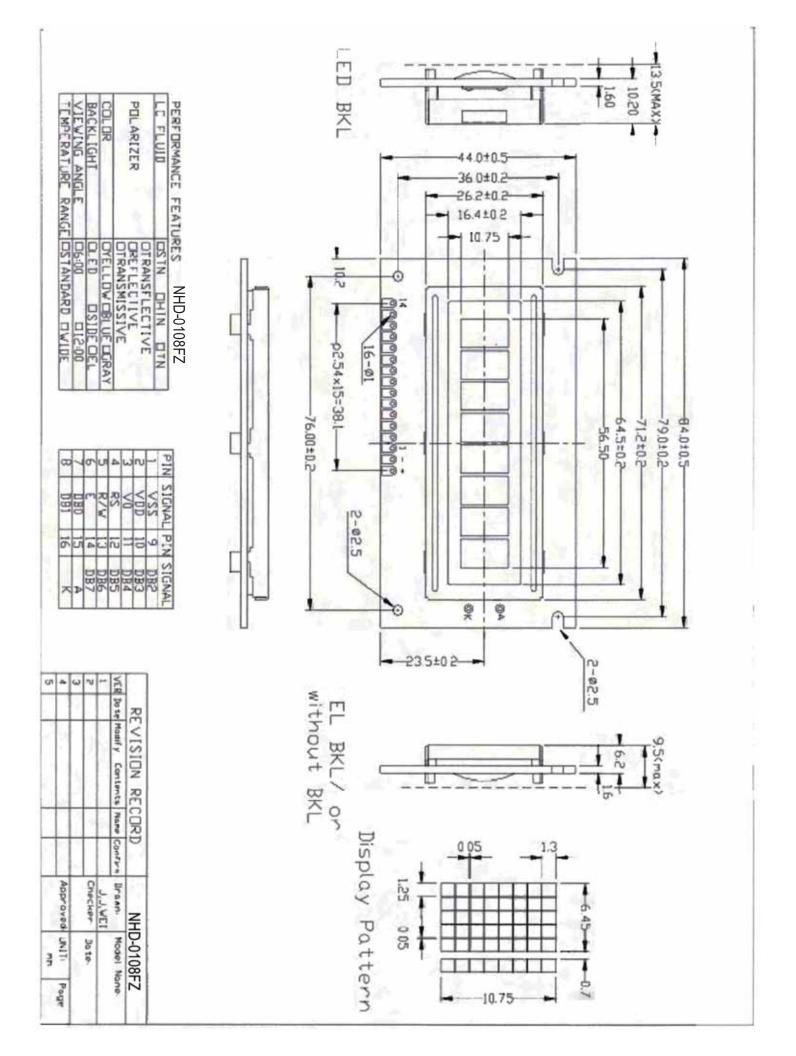

#### **Outline dimension**

## Absolute maximum ratings

| Item                        | Symbol                           |     | Standard |     | Unit |

|-----------------------------|----------------------------------|-----|----------|-----|------|

| Power voltage               | V <sub>DD</sub> -V <sub>SS</sub> | 0   | -        | 7.0 | V    |

| Input voltage               | VIN                              | VSS | -        | VDD | ·    |

| Operating temperature range | VOP                              | -20 | -        | +70 | ř    |

| Storage temperature range   | VST                              | -30 | -        | +80 |      |

<sup>\*</sup>Wide temperature range is available

(operating/storage temperature as  $-20 \sim +70/-30 \sim +80$ °C)

## Interface pin description

| Pin no. | Symbol      | External connection | Function                                                                                                                                                      |  |  |  |  |  |

|---------|-------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | $V_{ss}$    |                     | Signal ground for LCM (GND)                                                                                                                                   |  |  |  |  |  |

| 2       | $ m V_{DD}$ | Power supply        | Power supply for logic (+5V) for LCM                                                                                                                          |  |  |  |  |  |

| 3       | $V_0$       |                     | Contrast adjust                                                                                                                                               |  |  |  |  |  |

| 4       | RS          | MPU                 | Register select signal                                                                                                                                        |  |  |  |  |  |

| 5       | R/W         | MPU                 | Read/write select signal                                                                                                                                      |  |  |  |  |  |

| 6       | Е           | MPU                 | Operation (data read/write) enable signal                                                                                                                     |  |  |  |  |  |

| 7~10    | DB0~DB3     | MPU                 | Four low order bi-directional three-state data bus lines. Used for data transfer between the MPU and the LCM. These four are not used during 4-bit operation. |  |  |  |  |  |

| 11~14   | DB4~DB7     | MPU                 | Four high order bi-directional three-state data bus lines. Used for data transfer between the MPU                                                             |  |  |  |  |  |

| 15      | LED+        | LED BKL power       | Power supply for BKL (+4.2V)                                                                                                                                  |  |  |  |  |  |

| 16      | LED-        | supply              | Power supply for BKL (GND)                                                                                                                                    |  |  |  |  |  |

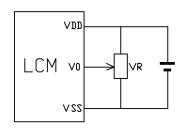

#### Contrast adjust

$V_{\text{DD}\sim}V_0\text{: LCD Driving voltage}$

VR: 10k~20k

#### **Optical characteristics**

TN type display module (Ta=25℃, VDD=5.0V)

| Item                 | Symbol      | Condition | Min. | Typ. | Max. | Unit         |

|----------------------|-------------|-----------|------|------|------|--------------|

| Viewing angle        | θ           | Cr≥4      | -25  | -    | -    | dea          |

|                      | Ф           | Cr ##4    | -30  | -    | 30   | deg          |

| Contrast ratio       | Cr          |           | -    | 2    | -    | -            |

| Response time (rise) | Tr          | -         | -    | 120  | 150  | <b>123</b> G |

| Response time (fall) | $T_{\rm r}$ | -         | -    | 120  | 150  | ms           |

STN type display module (Ta=25°C, VDD=5.0V)

| Item                 | Symbol      | Condition            | Min. | Тур. | Max. | Unit |

|----------------------|-------------|----------------------|------|------|------|------|

| Viewing angle        | θ           | Cr≥2                 | -60  | -    | 35   | dea  |

|                      | Φ           | Cr <sub>s</sub> ss 2 | -40  | -    | 40   | deg  |

| Contrast ratio       | Cr          |                      | _    | 6    | -    | -    |

| Response time (rise) | $T_{\rm r}$ | -                    | -    | 150  | 250  | mg   |

| Response time (fall) | $T_{\rm r}$ | -                    | -    | 150  | 250  | ms   |

### **Electrical characteristics**

DC characteristics

| Parameter                | Symbol           | Conditions                    | Min. | Тур. | Max.              | Unit |

|--------------------------|------------------|-------------------------------|------|------|-------------------|------|

| Supply voltage for LCD   | $V_{DD}$ - $V_0$ | Ta =25℃                       | -    | 4.6  | -                 | V    |

| Input voltage            | $V_{ m DD}$      |                               | 4.7  | -    | 5.5               |      |

| Supply current           | Idd              | Ta=25℃, V <sub>DD</sub> =5.0V | -    | 1.5  | 2.5               | mA   |

| Input leakage current    | Ilkg             |                               | -    | -    | 1.0               | uA   |

| "H" level input voltage  | Vih              |                               | 2.2  | -    | $V_{\mathrm{DD}}$ |      |

| "L" level input voltage  | VIL              | Twice initial value or less   | 0    | -    | 0.6               |      |

| "H" level output voltage | Voh              | LOH=-0.25mA                   | 2.4  | -    | -                 | V    |

| "L" level output voltage | Vol              | LOH=1.6mA                     | -    | -    | 0.4               |      |

| Backlight supply voltage | $V_{\rm F}$      |                               | -    | 4.2  | 4.6               |      |

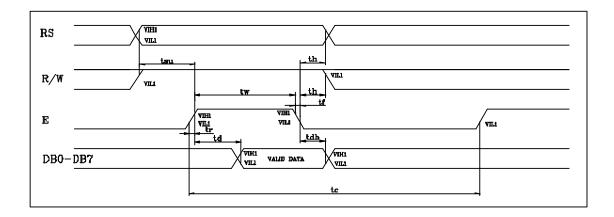

## **Read cycle** (Ta=25℃, VDD=5.0V)

| Parameter                 | Symbol      | Test pin | Min. | Тур. | Max. | Unit |

|---------------------------|-------------|----------|------|------|------|------|

| Enable cycle time         | <b>t</b> c  |          | 500  | -    | -    |      |

| Enable pulse width        | tw          | Е        | 300  | -    | -    |      |

| Enable rise/fall time     | tr, tf      |          | -    | -    | 25   |      |

| RS; R/W setup time        | <b>t</b> su | RS; R/W  | 100  | -    | -    | ns   |

| RS; R/W address hold time | th          | RS; R/W  | 10   | -    | -    | 113  |

| Read data output delay    | <b>t</b> d  | DB0~DB7  | 60   | -    | 90   |      |

| Read data hold time       | <b>t</b> dh | עסט∼טם/  | 20   | _    | -    |      |

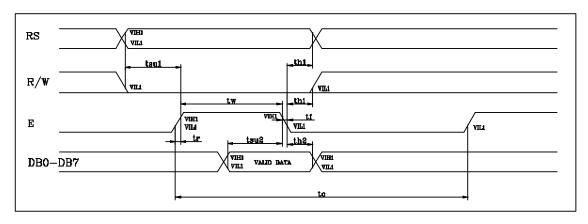

## Write cycle

| Parameter                 | Symbol       | Test pin | Min. | Тур. | Max. | Unit |

|---------------------------|--------------|----------|------|------|------|------|

| Enable cycle time         | tc           |          | 500  | -    | -    |      |

| Enable pulse width        | tw           | E        | 300  | -    | -    |      |

| Enable rise/fall time     | tr, tf       |          | -    | -    | 25   |      |

| RS; R/W setup time        | <b>t</b> su1 | RS; R/W  | 100  | -    | -    | ns   |

| RS; R/W address hold time | <b>t</b> h1  | RS; R/W  | 10   | -    | -    | 113  |

| Read data output delay    | <b>t</b> su2 | DB0~DB7  | 60   | -    | -    |      |

| Read data hold time       | th2          | עסט~טם/  | 10   | -    | -    |      |

## Write mode timing diagram

## Read mode timing diagram

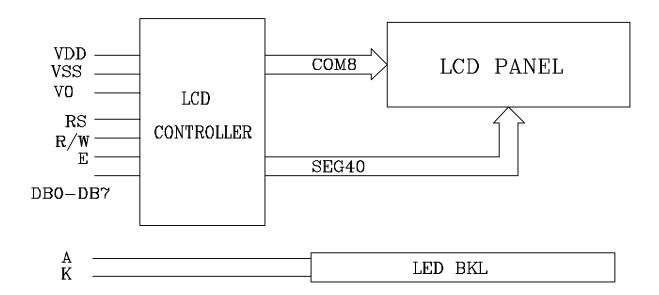

#### **Block diagram**

## **Instruction description**

#### **Outline**

To overcome the speed difference between the internal clock of KS0066U and the MPU clock, KS0066U performs internal operations by storing control in formations to IR or DR. The internal operation is determined according to the signal from MPU, composed of read/write and data bus (Refer to Table7).

Instructions can be divided largely into four groups:

- 1) KS0066U function set instructions (set display methods, set data length, etc.)

- 2) Address set instructions to internal RAM

- 3) Data transfer instructions with internal RAM

- 4) Others

The address of the internal RAM is automatically increased or decreased by 1.

Note: during internal operation, busy flag (DB7) is read "High".

Busy flag check must be preceded by the next instruction.

When an MPU program with checking the busy flag (DB7) is made, it must be necessary 1/2 fuss for executing the next instruction by the falling edge of the "E" signal after the busy flag (DB7) goes to "LOW".

#### **Contents**

#### 1) Clear display

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter).

Return cursor to the original status, namely, brings the cursor to the left edge on the fist line of the display. Make the entry mode increment (I/D="High").

#### 2) Return home

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | -   |

Return home is cursor return home instruction.

Set DDRAM address to "00H" into the address counter.

Return cursor to its original site and return display to its original status, if shifted.

Contents of DDRAM does not change.

#### 3) Entry mode set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | SH  |

Set the moving direction of cursor and display.

#### I/D: increment / decrement of DDRAM address (cursor or blink)

When I/D="high", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D="Low", cursor/blink moves to left and DDRAM address is increased by 1.

\*CGRAM operates the same way as DDRAM, when reading from or writing to CGRAM.

(I/D="high". shift left, I/D="Low". Shift right).

#### 4) Display ON/OFF control

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | C   | В   |

Control display/cursor/blink ON/OFF 1 bit register.

#### D: Display ON/OFF control bit

When D="High", entire display is turned on.

When D="Low", display is turned off, but display data remains in DDRAM.

#### C: cursor ON/OFF control bit

When D="High", cursor is turned on.

When D="Low", cursor is disappeared in current display, but I/D register preserves its data.

#### B: Cursor blink ON/OFF control bit

When B="High", cursor blink is on, which performs alternately between all the "High" data and display characters at the cursor position.

When B="Low", blink is off.

#### 5) Cursor or display shift

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 1   | S/C | R/L | -   | -   |

Shifting of right/left cursor position or display without writing or reading of display data.

This instruction is used to correct or search display data. (Refer to Table 6)

During 2-line mode display, cursor moves to the 2<sup>nd</sup> line after the 40<sup>th</sup> digit of the 1<sup>st</sup> line.

When display data is shifted repeatedly, each line is shifted individually.

When display shift is performed, the contents of the address counter are not changed.

#### Shift patterns according to S/C and R/L bits

| S/C | R/L | Operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, AC is decreased by 1                            |

| 0   | 1   | Shift cursor to the right, AC is increased by 1                           |

| 1   | 0   | Shift all the display to the left, cursor moves according to the display  |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

#### 6) Function set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | DL  | N   | F   | ı   | -   |

#### DL: Interface data length control bit

When DL="High", it mans 8-bit bus mode with MPU.

When DL="Low", it mans 4-bit bus mode with MPU. Hence, DL is a signal to select 8-bit or 4-bit bus mode.

When 4-but bus mode, it needs to transfer 4-bit data twice.

#### N: Display line number control bit

When N="Low", 1-line display mode is set.

When N="High", 2-line display mode is set.

#### F: Display line number control bit

When F="Low", 5x8 dots format display mode is set.

When F="High", 5x11 dots format display mode.

#### 7) Set CGRAM address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set CGRAM address to AC.

The instruction makes CGRAM data available from MPU.

#### 8) Set DDRAM address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC.

This instruction makes DDRAM data available form MPU.

When 1-line display mode (N=LOW), DDRAM address is form "00H" to "4FH".

In 2-line display mode (N=High), DDRAM address in the 1<sup>st</sup> line form "00H" to "27H", and DDRAM address In the 2<sup>nd</sup> line is from "40H" to "67H".

#### 9) Read busy flag & address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

This instruction shows whether KS0066U is in internal operation or not.

If the resultant BF is "High", internal operation is in progress and should wait BF is to be LOW, which by then if the nest instruction can be performed. In this instruction you can also read the value of the address counter.

#### 10) Write data to RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM.

The selection of RAM from DDRAM, and CGRAM, is set by the previous address set instruction (DDRAM address set, CGRAM address set).

RAM set instruction can also determine the AC direction to RAM.

After write operation. The address is automatically increased/decreased by 1, according to the entry mode.

#### 11) Read data from RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If the address set instruction of RAM is not performed before this instruction, the data that has been read first is invalid, as the direction of AC is not yet determined. If RAM data is read several times without RAM address instructions set before, read operation, the correct RAM data can be obtained from the second. But the first data would be incorrect, as there is no time margin to transfer RAM data. In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction, It also transfers RAM data to output data register.

After read operation, address counter is automatically increased/decreased by 1 according to the entry mode.

After CGRAM read operation, display shift may not be executed correctly.

NOTE: In case of RAM write operation, AC is increased/decreased by 1 as in read operation.

At this time, AC indicates next address position, but only the previous data can be read by the read instruction.

#### **Instruction table**

|                                  |    |         |     | Ins | structi | ion co | de  |     |     |     |                                                                                                                                              | Execution              |

|----------------------------------|----|---------|-----|-----|---------|--------|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Instruction                      | RS | R/<br>W | DB7 | DB6 | DB5     | DB4    | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                                  | Time (fosc=<br>270 KHZ |

| Clear<br>Display                 | 0  | 0       | 0   | 0   | 0       | 0      | 0   | 0   | 0   | 1   | Write "20H" to DDRA and set<br>DDRAM address to "00H"<br>from AC                                                                             | 1.53ms                 |

| Return<br>Home                   | 0  | 0       | 0   | 0   | 0       | 0      | 0   | 0   | 1   | -   | Set DDRAM address to "00H"<br>From AC and return cursor to<br>Its original position if shifted.<br>The contents of DDRAM are<br>not changed. | 1.53ms                 |

| Entry mode<br>Set                | 0  | 0       | 0   | 0   | 0       | 0      | 0   | 1   | I/D | SH  | Assign cursor moving direction And blinking of entire display                                                                                | 39us                   |

| Display ON/<br>OFF control       | 0  | 0       | 0   | 0   | 0       | 0      | 1   | D   | С   | В   | Set display (D), cursor (C), and<br>Blinking of cursor (B) on/off<br>Control bit.                                                            |                        |

| Cursor or<br>Display shift       | 0  | 0       | 0   | 0   | 0       | 1      | S/C | R/L | -   | -   | Set cursor moving and display<br>Shift control bit, and the<br>Direction, without changing of<br>DDRAM data.                                 | 39us                   |

| Function set                     | 0  | 0       | 0   | 0   | 1       | DL     | N   | F   | -   | -   | Set interface data length (DL: 8-Bit/4-bit), numbers of display<br>Line (N: =2-line/1-line) and,<br>Display font type (F: 5x11/5x8)          | 39us                   |

| Set CGRAM<br>Address             | 0  | 0       | 0   | 1   | AC5     | AC4    | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address Counter.                                                                                                        | 39us                   |

| Set DDRAM<br>Address             | 0  | 0       | 1   | AC6 | AC5     | AC4    | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address Counter.                                                                                                        | 39us                   |

| Read busy<br>Flag and<br>Address | 0  | 1       | BF  | AC6 | AC5     | AC4    | AC3 | AC2 | AC1 | AC0 | Whether during internal Operation or not can be known By reading BF. The contents of Address counter can also be read.                       | 0us                    |

| Write data to<br>Address         | 1  | 0       | D7  | D6  | D5      | D4     | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM).                                                                                                  | 43us                   |

| Read data<br>From RAM            | 1  | 1       | D7  | D6  | D5      | D4     | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM).                                                                                                   | 43us                   |

NOTE: When an MPU program with checking the busy flag (DB7) is made, it must be necessary 1/2fosc is necessary for executing the next instruction by the falling edge of the "E" signal after the busy flag (DB7) goes to "Low".

#### DDRAM address:

Display position

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----|----|----|----|----|----|----|----|

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

DDRAM address

## Standard character pattern

| Upper 4    |                  |      |      |      |      |      |      |          |      |      |      |         |      |          |            |      |

|------------|------------------|------|------|------|------|------|------|----------|------|------|------|---------|------|----------|------------|------|

| Lower Bits | 0000             | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111     | 1000 | 1001 | 1010 | 1011    | 1100 | 1101     | 1110       | 1111 |

| xxxx0000   | CG<br>RAM<br>(1) |      |      | 0    | a    | P    | *    | P        |      |      |      |         | 7    | =        | ŏ          | þ    |

| xxxx0001   | (2)              |      | İ    | 1    | A    | Q    | a    | 9        |      |      | 0    | P       | 手    | 4        | Û:         | T    |

| xxxx0010   | (3)              |      | 11   | 2    | B    | R    | Ь    | r        |      |      | r    | 4       | ij   | ×        | F          | 0    |

| xxxx0011   | (4)              |      | #    | 3    | C    | 5    | C    | 5        |      |      |      | Ċ       | 丁    | E        | Ð          | 67   |

| xxxx0100   | (5)              |      | \$   | 4    | D    | T    | d    | t,       |      |      | ٠,   | I       | F    | t        | Н          | 25   |

| xxxx0101   | (6)              |      | 74   | 5    | E    | U    | 8    | u        |      |      |      | 7       | ナ    | ュ        | Ю          | ü    |

| xxxx0110   | (7)              |      | 8    | 6    | F    | Ų    | f    | Ų        |      |      | ヲ    | 力       | _    | 3        | Q.         | Ы    |

| xxxx0111   | (8)              |      | 7    | 7    | G    | Ш    | 9    | W        |      |      | 7    | <u></u> | X    | <b>ラ</b> | 9          | Л    |

| xxxx1000   | (1)              |      | (    | 8    | H    | X    | h    | X        |      |      | 4    | 7       | 末    | IJ       | Ļ          | X    |

| xxxx1001   | (2)              |      | )    | 9    | I    | Y    | i    | ¥        |      |      | ÷    | Ţ       | Ļ    | ΙĿ       | -1         | y    |

| xxxx1010   | (3)              |      | *    |      | J    | Z    | į    | Z        |      |      | I    |         | ιì   | Į,       | <b>'</b> " | #    |

| xxxx1011   | (4)              |      | +    | 7    | K    |      | k    | €        |      |      | 才    | ţ       | E    |          | X          | Ķ    |

| xxxx1100   | (5)              |      | 7    | <    |      | ¥    | 1    |          |      |      | †7   | ij      | J    | ņ        | ÷          | Ħ    |

| xxxx1101   | (6)              |      |      |      | M    | ]    | M    | }        |      |      | ュ    | Z       | ጎ    | ->       | ¥          | +    |

| xxxx1110   | (7)              |      |      | >    | H    | e**4 | h    | <b>+</b> |      |      | 3    | t       | 市    | ***      | ñ          |      |

| xxxx1111   | (8)              |      | ,,** | ?    | 0    |      | 0    | +        |      |      | •4   | IJ      | 7    | 0        | Ö          |      |